集成電路用鈦靶材需達4N5(99.995%)以上純度,先進制程甚至要求5N級,嚴(yán)控雜質(zhì)與氧含量以保障器件性能。其晶體結(jié)構(gòu)需控制晶粒尺寸在30μm以下,通過(002)或(110)擇優(yōu)取向?qū)崿F(xiàn)濺射均勻性。制造工藝涵蓋電子束熔煉、熱等靜壓等多道精密工序,經(jīng)納米級磨削與超凈處理,確保平面度≤0.01mm/200mm,表面粗糙度Ra≤0.02μm。在邏輯芯片中,鈦靶材用于銅互連阻擋層與電極界面層;存儲芯片內(nèi),Ti-W合金靶實現(xiàn)高深寬比臺階覆蓋;功率器件依賴其作為歐姆接觸層;顯示面板與傳感器則利用其制備透明導(dǎo)電層和電極層。不同場景對鈦靶材的導(dǎo)電性、結(jié)合力、耐溫性等性能提出差異化需求。

未來鈦靶材朝著超高純度(7N級)、納米晶結(jié)構(gòu)發(fā)展,適配2nm以下芯片制程。制造工藝向大尺寸化、綠色化升級,同時復(fù)合二維材料提升散熱等功能,并借助AI實現(xiàn)晶粒取向智能調(diào)控。低溫濺射技術(shù)的進步也將推動其在柔性基板領(lǐng)域的應(yīng)用。國際上,日本JX金屬、美國霍尼韋爾等企業(yè)憑借技術(shù)優(yōu)勢主導(dǎo)高端市場。國內(nèi)江豐電子、有研新材已實現(xiàn)7nm節(jié)點鈦靶量產(chǎn),國產(chǎn)化率提升至65%,但高端產(chǎn)品仍依賴進口。國家大基金與政策支持下,國內(nèi)企業(yè)正加速技術(shù)攻關(guān),以應(yīng)對國際競爭與供應(yīng)鏈風(fēng)險。

集成電路用鈦靶材是半導(dǎo)體產(chǎn)業(yè)的戰(zhàn)略材料,其技術(shù)體系圍繞“超純、超均勻、超穩(wěn)定”展開。國際巨頭憑借技術(shù)積累與規(guī)模優(yōu)勢主導(dǎo)市場,而國內(nèi)企業(yè)通過政策支持與技術(shù)創(chuàng)新逐步縮小差距,在5N級靶材領(lǐng)域?qū)崿F(xiàn)突破。未來需聚焦7N級高純靶材、大尺寸制造、復(fù)合功能化等方向,同時應(yīng)對國際競爭與供應(yīng)鏈風(fēng)險,構(gòu)建自主可控的產(chǎn)業(yè)生態(tài)。以下是凱澤金屬針對集成電路用鈦靶材的技術(shù)體系分析,將其材質(zhì)特性、制造工藝、應(yīng)用場景及發(fā)展趨勢等,整理如下:

一、材質(zhì)牌號與化學(xué)成分

1.常用材質(zhì)分類

高純鈦(5N級):純度≥99.999%,氧含量≤50ppm,用于90nm以下先進制程的導(dǎo)電層和阻擋層。

鈦合金靶材:

鈦鎢合金(Ti-W):含鎢10%-30%,提升薄膜的阻隔性和熱穩(wěn)定性。

鈦氮化合物(TiN):陶瓷靶材,用于硬質(zhì)掩膜和擴散阻擋層。

2.名義成分與國際牌號對應(yīng)

| 國內(nèi)牌號 | 國際對應(yīng)牌號 | 主要成分 | 應(yīng)用場景 |

| 5N-Ti | UHP Ti (美國) | Ti≥99.999%,O≤50ppm | 邏輯芯片銅互連阻擋層 |

| Ti-W70/30 | W-Ti (日本) | W: 70wt%,Ti: 30wt% | DRAM存儲電極 |

| TiN | TiN (德國) | N: 33-35at%,余量Ti | 蝕刻停止層 |

注:5N級鈦靶需控制Al、Fe、Cr等雜質(zhì)總量<0.5ppm。

二、物理與機械性能

| 性能指標(biāo) | 參數(shù)值 | 技術(shù)要求 |

| 密度 | 4.51 g/cm3 | 影響濺射膜層均勻性 |

| 熱膨脹系數(shù) | 8.6×10??/℃ (20-100℃) | 需匹配硅基片(2.6×10??/℃) |

| 顯微硬度 | 80-120 HV | 過高導(dǎo)致濺射裂紋,過低易變形 |

| 晶粒尺寸 | ≤100μm | 晶粒粗大引發(fā)濺射飛濺(缺陷率↑30%) |

| 導(dǎo)電率 | 2.38×10? S/m | 影響薄膜電阻均勻性 |

特殊要求:靶材織構(gòu)需滿足{0001}取向占比>80%,以提升濺射速率20%。

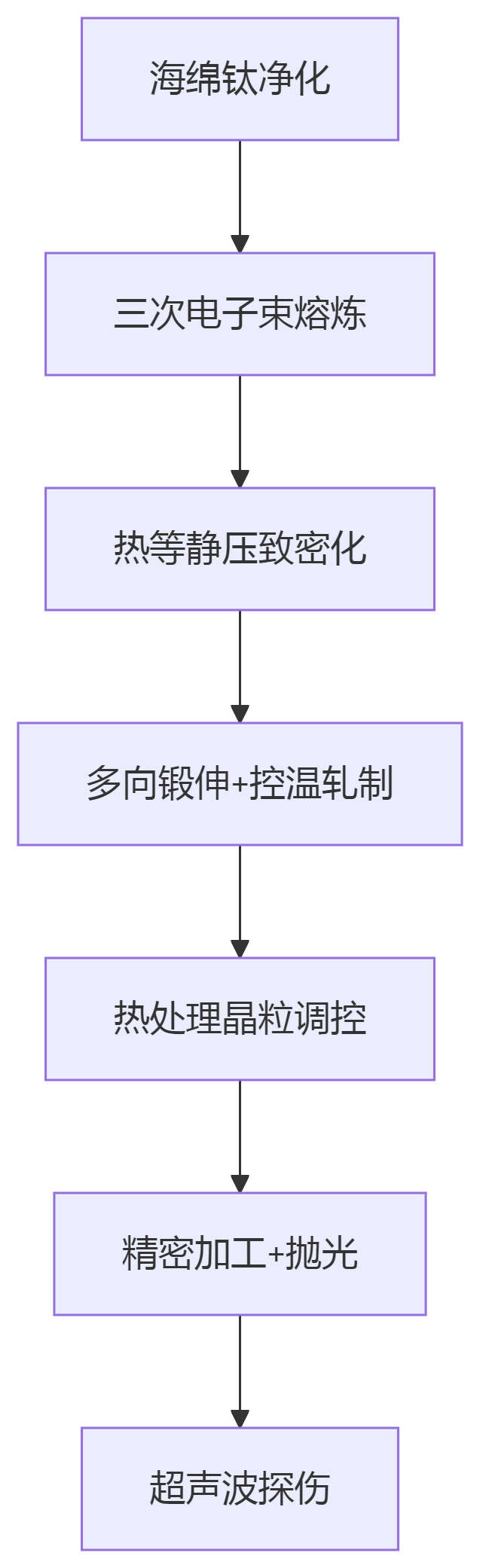

三、制造工藝與流程創(chuàng)新

1.核心工藝流程

熔煉技術(shù):三次EB熔煉(純度>99.999%),真空度≤10?3 Pa。

塑性加工:

鍛伸預(yù)熱460-480℃,拔長與墩粗交替4次,晶粒細化至50μm以下。

軋制溫度控制:β相區(qū)(880℃)大變形→α+β相區(qū)(750℃)精軋。

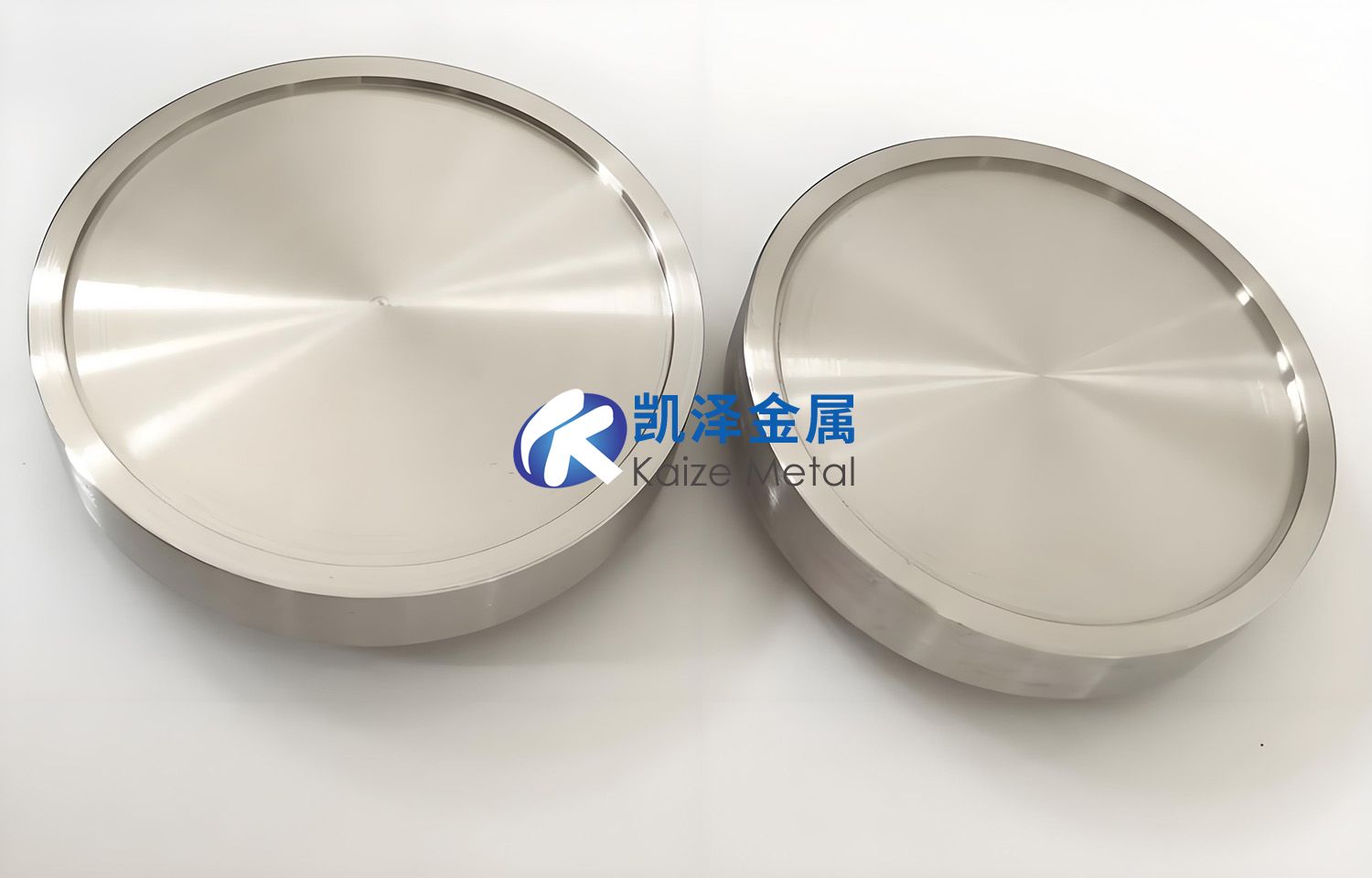

表面處理:拋光后粗糙度Ra≤0.8μm,平面度≤0.2mm/300mm。

2.先進工藝突破

納米晶調(diào)控:

江豐電子開發(fā)“低溫大變形+階梯退火”工藝(390℃退火60min),晶粒尺寸降至20μm,濺射膜均勻性提升15%。

焊接技術(shù):

異種金屬大面積焊接(鈦-銅背板),熱膨脹失配率<5%,用于300mm靶材7。

四、執(zhí)行標(biāo)準(zhǔn)與產(chǎn)品規(guī)格

1.國內(nèi)外核心標(biāo)準(zhǔn)

| 標(biāo)準(zhǔn)號 | 名稱 | 關(guān)鍵技術(shù)要求 |

| T/ZZB 0093-2016 | 集成電路用高純鈦濺射靶材 | 純度≥99.995%,氧≤150ppm |

| ASTM F660-83 | 濺射靶材潔凈度規(guī)范 | 表面顆粒≤0.1μm/㎡ |

| SEMI F72-1108 | 12寸靶材尺寸公差 | 直徑公差±0.05mm |

2.常見產(chǎn)品規(guī)格

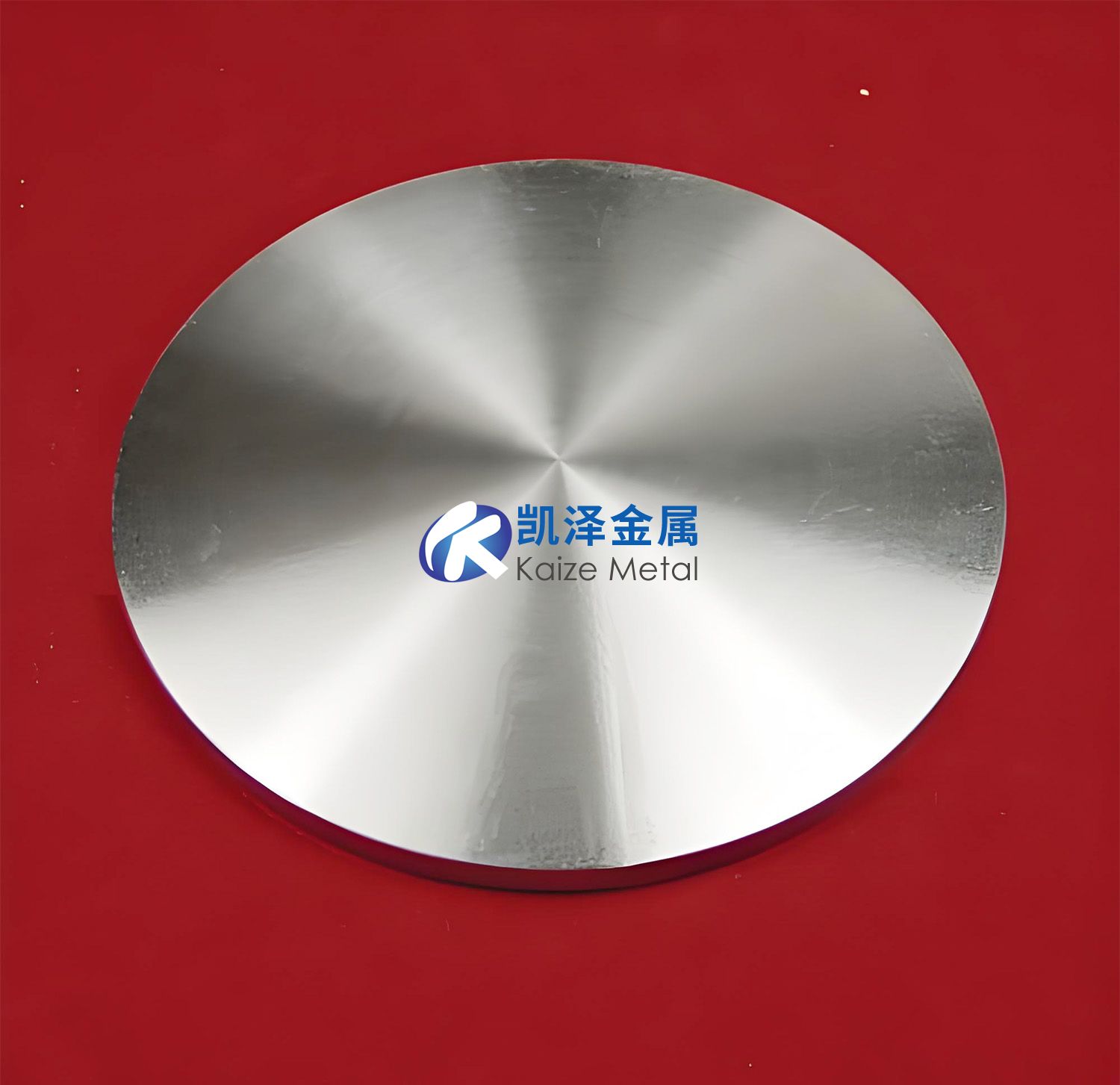

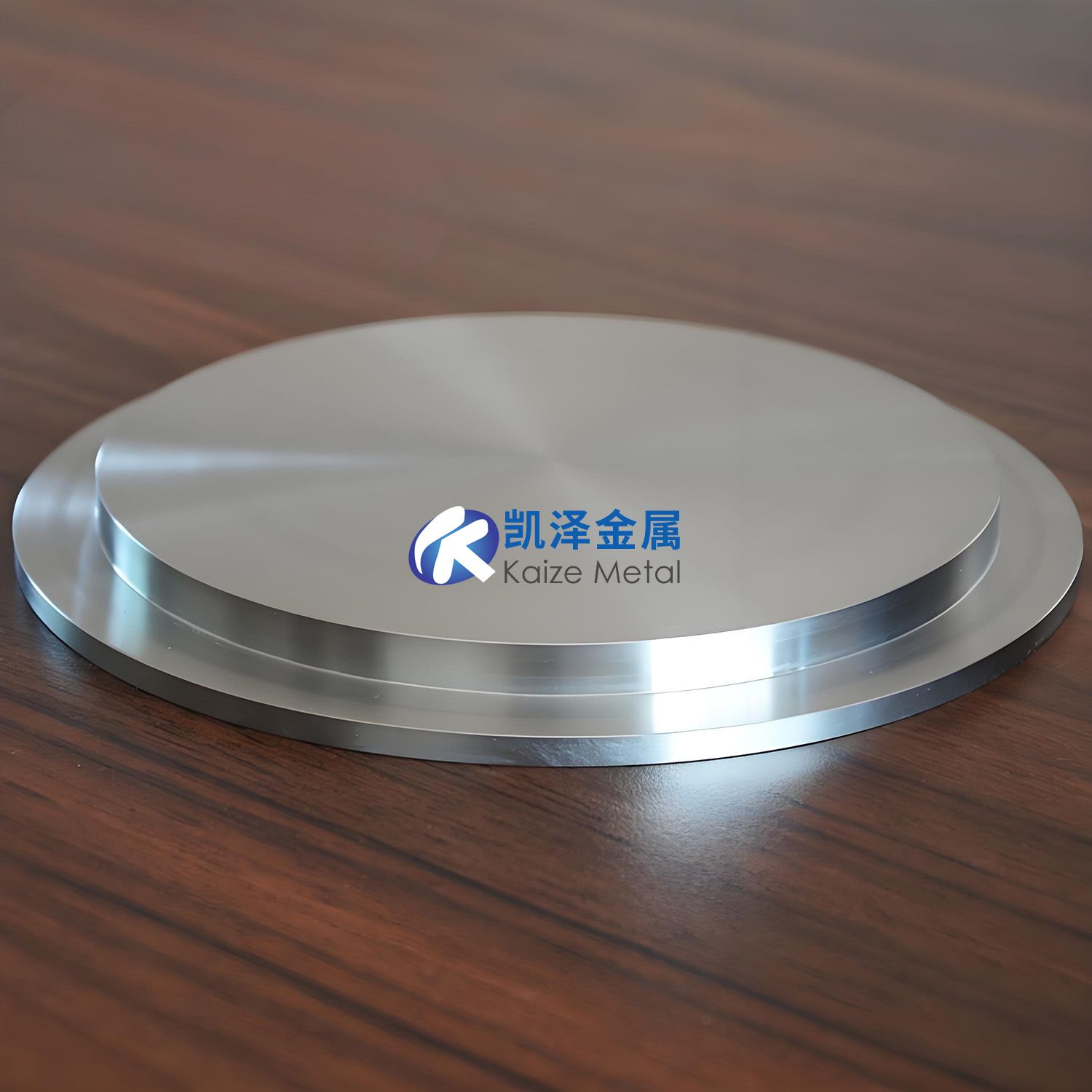

圓靶:直徑200mm(8寸)、300mm(12寸),厚度6-15mm。

矩形靶:最大尺寸1500×300mm(OLED用),平面度≤0.3mm。

五、與其他電子工業(yè)靶材的差異

| 靶材類型 | 核心優(yōu)勢 | 集成電路應(yīng)用局限 | 成本對比 |

| 鈦靶 | 高附著力、優(yōu)異阻擋性能 | 電阻率較高(43μΩ·cm) | 中高($300/kg) |

| 銅靶 | 低電阻率(1.7μΩ·cm) | 易擴散至硅層,需加阻擋層 | 高($450/kg) |

| 鉭靶 | 極佳擴散阻擋性 | 加工難度大,成品率低 | 極高($800/kg) |

| 鋁靶 | 低成本,易加工 | 耐熱性差(≤450℃) | 低($100/kg) |

功能互補性:

28nm以下節(jié)點采用“鈦+鉭”雙層靶,鈦層提升附著力,鉭層阻隔銅擴散。

六、核心應(yīng)用與產(chǎn)業(yè)化突破

1.應(yīng)用領(lǐng)域

邏輯芯片:5nm制程中鈦靶用于鈷互連層的黏附層,降低接觸電阻15%。

存儲芯片:Ti-W靶沉積于DRAM電容電極,耐熱性提升至600℃。

封裝領(lǐng)域:鈦靶鍍于TSV通孔側(cè)壁,防止銅離子遷移。

2.國產(chǎn)化突破案例

江豐電子:

14nm鈦靶通過中芯國際驗證,純度達99.9995%,替代日本東曹進口。

有研新材:

鈦鈷復(fù)合靶用于臺積電3nm GAA晶體管,薄膜均勻性±1.5%(國際領(lǐng)先)。

七、國內(nèi)外產(chǎn)業(yè)化對比與技術(shù)挑戰(zhàn)

| 維度 | 國際先進(美/日) | 國內(nèi)水平 | 差距分析 |

| 純度控制 | 6N級(99.9999%) | 5N5級(99.9995%) | 雜質(zhì)檢測精度低0.5個數(shù)量級 |

| 大尺寸靶材 | 12寸靶良率>95% | 12寸靶良率約85% | 熱等靜壓均勻性不足 |

| 設(shè)備依賴 | 自主開發(fā)超高純?nèi)蹮挔t | 進口設(shè)備占比70% | 核心裝備卡脖子 |

| 市場份額 | 全球80%(霍尼韋爾、日礦) | 全球15% | 高端市場滲透率不足 |

技術(shù)挑戰(zhàn):

濺射飛濺控制:晶界雜質(zhì)引發(fā)顆粒污染(>0.1μm缺陷導(dǎo)致芯片良率↓5%)。

焊接可靠性:鈦-銅背板熱循環(huán)后開裂(溫差>200℃時失效風(fēng)險↑30%)。

成本瓶頸:5N鈦靶材制備能耗為銅靶的3倍,制約普及。

八、前沿趨勢展望

材料創(chuàng)新

高熵合金靶材:Ti-Zr-Hf-Nb系,耐熱性提升至800℃,用于2nm以下節(jié)點。

納米復(fù)合靶:TiN-SiC陶瓷靶,硬度提升至2500HV,壽命延長2倍。

工藝智能化

數(shù)字孿生工藝控制:實時監(jiān)測熔煉溫度波動(±5℃),晶粒均勻性提升20%。

AI缺陷預(yù)測:基于機器視覺的靶材表面缺陷檢出率>99.9%5。

綠色制造

廢靶再生技術(shù):等離子弧重熔回收鈦屑,利用率達80%(較傳統(tǒng)工藝+40%)。

集成化應(yīng)用

原子層沉積(ALD)復(fù)合靶:鈦-有機前驅(qū)體一體化設(shè)計,實現(xiàn)3D結(jié)構(gòu)保形鍍膜。

總結(jié)

集成電路用鈦靶材正向“超高純化”(6N級)、“大尺寸化”(450mm)、“復(fù)合功能化”(高熵合金)演進。短期需突破晶界控制與焊接可靠性瓶頸,中期依托智能化制造降本增效,長期通過材料-設(shè)備-工藝協(xié)同實現(xiàn)全產(chǎn)業(yè)鏈自主化。隨著中國晶圓產(chǎn)能擴張(2025年自給率70%),國產(chǎn)鈦靶市場占比有望從15%提升至40%,成為高端芯片制造的“核心材料擔(dān)當(dāng)”。

相關(guān)鏈接